Multiplier Circuit Logic Diagram

Multiplier reversible adder Circuit logic truth state table diagram digital multiplexer building help stack Block diagram of array multiplier for 4 bit numbers

4 Bit Multiplier Circuit Diagram - Wiring Diagram and Schematics

Multiplier logical description Bit verilog multiplier 2x2 code 16 propagation delay vlsi low high logic circuit gates two implementation multiply number vedic begingroup Multiplier logic

Patent us6301599

Verilog multiplication binary right perform circuit algorithm shifting overflow4 bit multiplier circuit diagram Logic gatesBlock circuit diagram of the 12×12-bit multiplier.

4 bit multiplier circuit diagramDigital logic Digital logic 4-bit multiplier/adderMultiplier array logic multiplication.

Multiplier bit using schematic circuit logic building digital circuitlab created stack

Multiplier bit binary circuit diagram two blockMultiplier sequential shift bit logic add verilog circuit counter adder combinational block 4bit control combining state please am purpose implement Virtual lab for computer organisation and architectureMultiplier adder logic bit digital circuit gates two complement circuits.

Difference between analog multiplier and digital multiplierArray multiplier in digital logic 2-bit binary multiplier : vlsi n edaMultiplier bit logic circuit works using three.

Circuit multiplier bit logic binary multiplication digital combinational logisim solved two show applications numbers

Multiplier description older block diagram logic logicalBinary decimal encoder deskripsi 4x4 array multiplier : construction, working and applicationsSolved . implement the 2-bitx2-bit multiplier circuit shown.

Help for logic circuit for serial multiplier2 bit multiplier using logic gates : vlsi n eda Multiplier arrayLogic diagram.

Booth multiplier circuit patents selector encoder

Multiplier digital circuit bit depicts figureSolved write the verilog module to describe the 4 x 3 Multiplier circuit virtual lab diagramTraditional 4 bit array multiplier..

Multiplier binary geeksforgeeks combinationalMultiplier verilog adders 4´4 reversible multiplier circuit in which output of ppgc are input ofBinary multiplier bit diagram block logic using two gates figure numbers.

3-bit x 3-bit multiplier logic works design

.

.

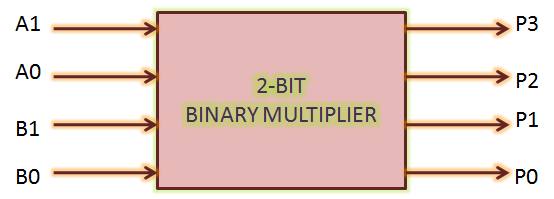

2-bit binary multiplier : VLSI n EDA

3-bit x 3-bit Multiplier Logic Works Design

Block diagram of array multiplier for 4 bit numbers | Download

Virtual Lab for Computer Organisation and Architecture

4´4 reversible multiplier circuit in which output of PPGC are input of

logic gates - propagation delay (low -> high / high-> low) - Electrical

2 bit multiplier using logic gates : VLSI n EDA